实验四 基于NIOS的软核设计实验二

实验4.1 Nios软核的设计

一、实验目的

了解NIOSII软核的设计方法。

二、实验步骤

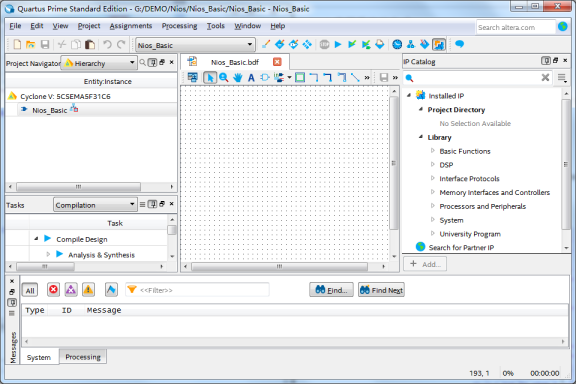

1、创建工程文件

首先创建一个工程Nios_Basic,因为Platform Designer的打开必须基于一个工程。

2、使用Platform Designer

Platform Designer允许用户创建一个Nios II系统模块,或者创建多主设备QSYS模块。一个完整的Nios II系统模块包含Nios II处理器和与之相关的系统外设。

Platform Designer会提示用户设置参数,Nios II系统模块一旦生成,就可以在QuartusII中作为一个器件被调用。

步骤:

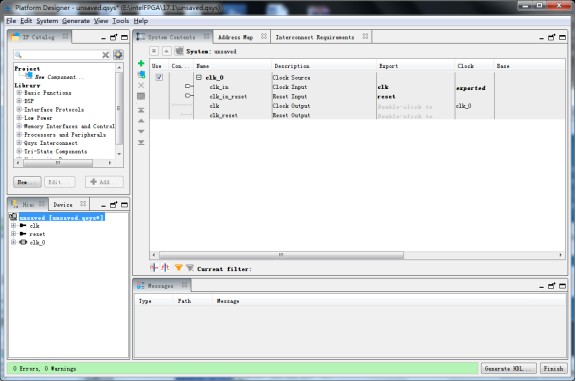

(1)在QuartusII中选择Tools/Platform Designer,来打开Platform Designer;

- 创建Nios II软核处理器系统,如图。

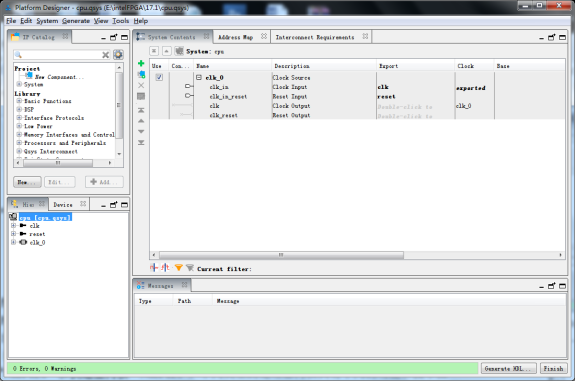

- 选择File-save,将文件保存为cpu如图所示;

- 添加组件(Nios II软核处理器、uart-RS232、On-Chip Memory)

�������� 配置Nios II软核处理器系统

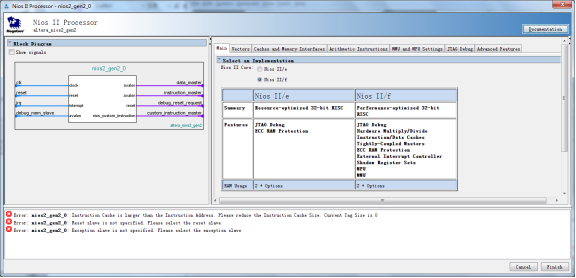

Nios II 软核处理器系统配置窗口的“Processors and Peripherals”选项卡中,双击Embedded Processors下的Nios II Processor,弹出Nios II Processor配置选项卡;

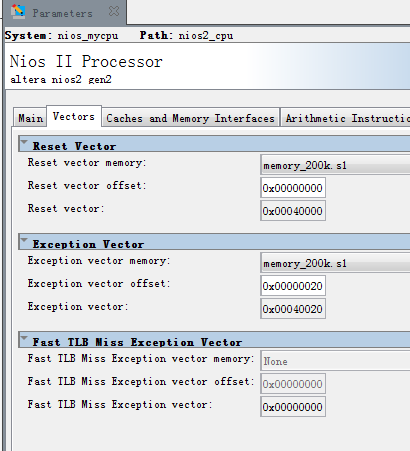

配置软核处理器,新一代Nios II 软核处理器有2种类型:经济型内核“Nios II/e”和快速型内核“Nios II/f”。不同类型的处理器内核具有不同的功能和技术指标,当然在获得强功能和高技术指标的同时也需要付出较多的逻辑资源,同时使用过程也变得复杂,这里本实验我们选用快速型内核“Nios II/f”。此时复位矢量“Reset Vector”和异常矢量“Exception Vector”无效,必须在指向的存储器及地址在完成存储器配置之后才能设置。其它选项暂不做任何处理即可。

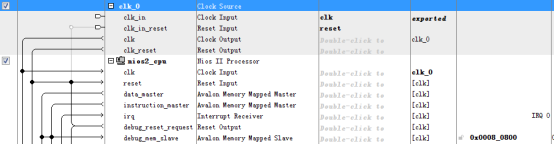

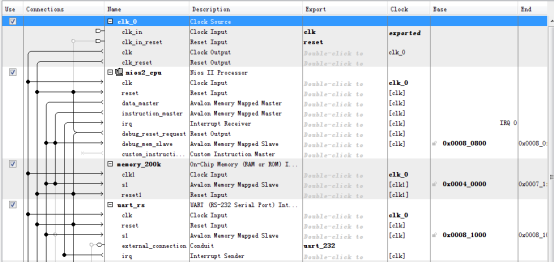

单击Finish, 回到如图7-7所示的界面,此时系统中已经具有了处理器nios2_gen2_0,并且IRQ以及Base address已经分配完成,用户可以在完全创建完整个QSYS系统后由Platform Designer进行统一重新分配,也可以根据自己需要分配。对nios2_gen2_0,clk_0右击Rename进行重命名为nios2_cpu,clk_0。

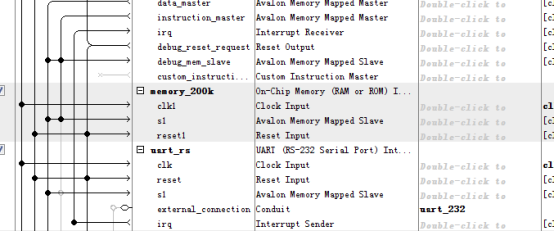

�������� 添加UART (RS-232 Serial Port) Intel FPGA IP

在组件选择栏中选择Interface Protocols ----Serial----UART (RS-232 Serial Port) Intel FPGA IP,点击Finish,右击Rename进行重命名为添加uart_rs.

添加输出端口,在Export列,在uart rs-232的external_connection 处双击,键入uart_232

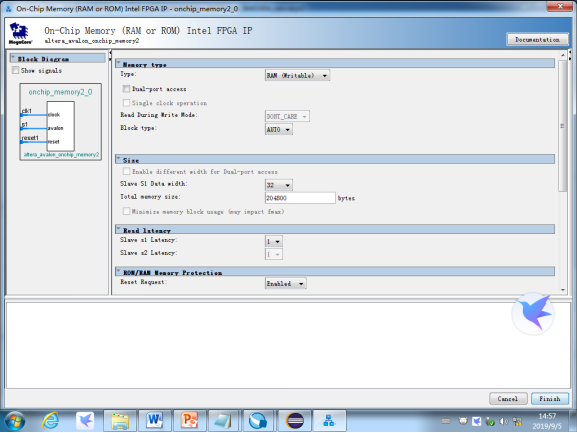

�������� 添加On-Chip Memory

在组件选择栏中选择Basic Functions ----On-Chip Memory(Ram or Rom)添加,

更改名称为memory_200k, 设置如上图:

注意:Total Memory Size设置为200K

- 连接添加的组件

完成了所有的组件添加以后我们需要对每个组件进行重命名。可以任意命名,我们尽量给出每个硬件外设的描述名称,因为在编写后面的用户程序中,我们会用到这些名称。

添加完了组件以后,这里我们还需要手动连线,这里我们可以遵循以下规则:数据主端口连接存储器和外设元件,而指令主端口只连接存储器元件。因此,我们可以按照上述规则进行如下连线,

- 如果是存储器类 IP 核,比如 on-chip memory、SDRAM 等,我们需要将其 S1(Avalon Memory Mapped Slave )端口连接到 Nios II 处理器核的data_master 和 instruction_master 端口上,

- 如果是非存储器 IP 核,比如 PIO 外设,或者是System ID 和 JTAG UART 等,我们只需要将其S1或其它名称( Avalon Memory Mapped Slave) 端口连接到Nios II 处理器核的 data_master 端口上即可。

- 对于时钟端口和复位端口,我们需要全部连接。时钟信号通过clk_0组件中clk_in接入Qsys中,板载时钟是50MHz,其它组件的时钟频率都使用clk_0中的clk,可直接点击连线端完成连线。

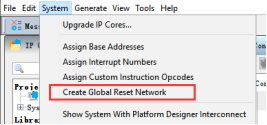

- 连接好时钟信号后,复位信号我们只需要在System中,选择Create Global Reset Network,复位连线就可以连接完成。

- 连接中断信号,对于添加的组件中jtug_uart、timer和key组件有Interrupt Sender端口,我们需要把它们连接到nios_procesor中irq端口(Interrupt Receiver)。连接完成后如下图所示。

注意:在Export这一栏中增加了reset、clk、uart_232的端口,这几个端口的作用是引出Nios II系统,具体的操作只需要在需要引出的端口上面双击即可,名字可以任意修改。

- 双击nios_procesor进入到Nios ii processor中设置Reset Vector和Exception Vetor,均选择on-chip memory,点击Finish。

- 自动为系统分配首地址和末地址

•�������� 这时本实验用到的IP核都已经添加完毕,但是在SOPC Builder最下方会出现错误提示,意思是上面添加的IP核的地址有冲突;

•�������� 我们不必要一个一个地修改首地址和末地址,点击System下拉菜单中 Assign Base Address ,软件就会自动为系统分配首地址和末地址。

•�������� 点击System下拉菜单中 Assign Interrupt Numbers

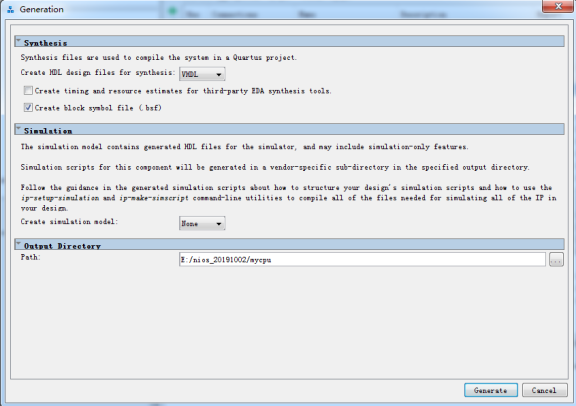

- 生成系统

点击“Generate”(Generate HDL...)为系统生成HDL文件和原理图模型,前者可以在HDL顶层文件中直接调用,后者可以在原理图中作为一个元件来调用。

出现Save System: completed successfully. 点击close出现Generate界面,出现Generate: completed successfully。点击Close,完成

出现Save System: completed successfully. 点击close出现Generate界面,出现Generate: completed successfully。点击Close,完成

实验4.2 QSYS应用系统的生成

一、实验目的

将设计好的器件添加到工程文件中并生成QSYS系统。

二、实验步骤

1. 单击File-New下Block Diagram/Schematic File,出现如图7-22界面,顶层文件名为Nios_Basic.bdf。同时产生工程文件Nios_Basic.qpf

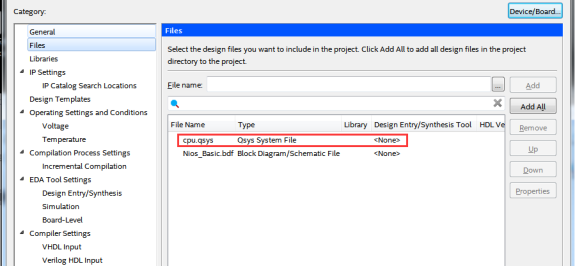

2.单击菜单Assignment下Setting,出现如图7-23界面,在Files类目按照如图添加路径G:\DEMO\Nios\Nios_Basic\cpu.qsys。

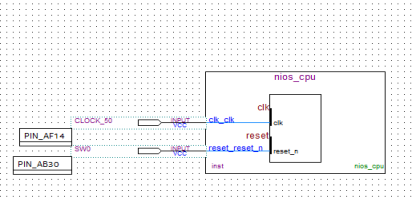

1. 双击空白处,在Project下添加所设计cpu系统模块,OK后,点击模块右键选取generate pin for symbol ports,并修改端口名。(如果找不到,可以搜索上一步形成的.qsys文件)

4.编译工程,之后为所有的I/O添加引脚,再次编译。

现在就可以将编译好的SOF文件通过JTAG口下载到FPGA中(注意下载时被配置复位键需处于无效状态)。

实验4.3 Nios II软核验证以及Nios II IDE软件的介绍

一、实验目的

当QSYS系统被下载进FPGA中后,就可以在系统中运行编写的应用程序了,通过本实验掌握Nios II Eclipse软件的使用并验证Nios II软核的存在。

二、实验步骤

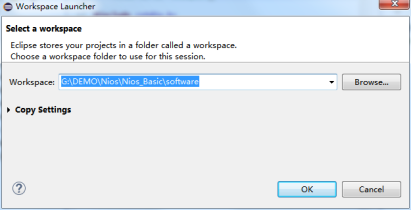

1 在开始/程序/Intel FPGA 17.1.0.590 Standard Edition/Nios II EDS 17.1.0.590启动Nios II Software Build Tools for Eclipse (Quartus Prime 17.1),设定Workspace工作目录,让此硬件所配合的软件存放在此目录中。进入Nios II 编译环境(进行C语言程序的编辑、编译和调试的界面)。

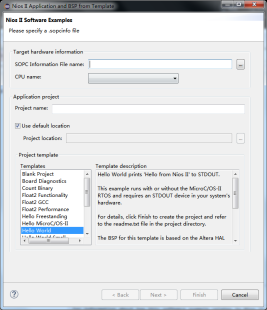

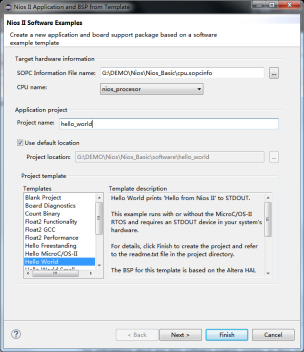

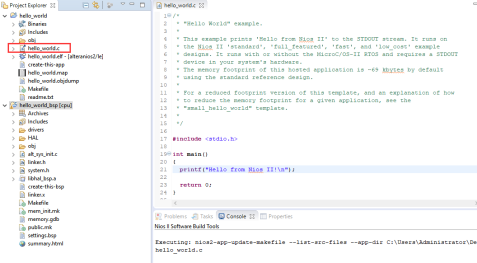

2由Nios II菜单File-New- Nios II Application and BSP from Template打开新工程

设置窗口,选中Hello World测试程序,如图7-32所示。

3.在 Target Hardware information中选择sopcinfo文件,并输入软件工程名hello_world。

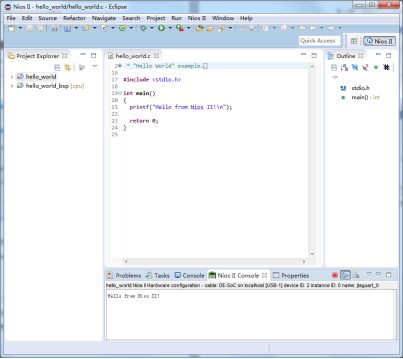

4.单击Finish,Hello World测试程序hello_world.c就在窗口中。

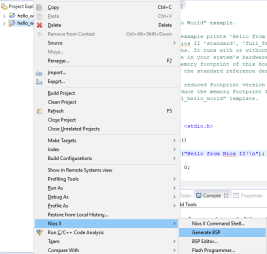

5.选择hello_world_bsp,在右键菜单中选择Nios II/Generate BSP。

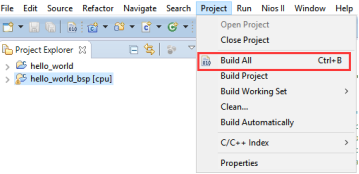

完成之后,选择Project/Build All,等待编译完成。

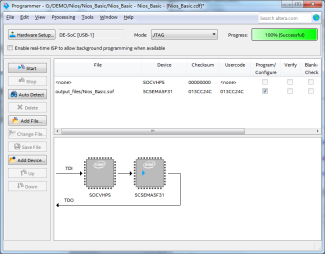

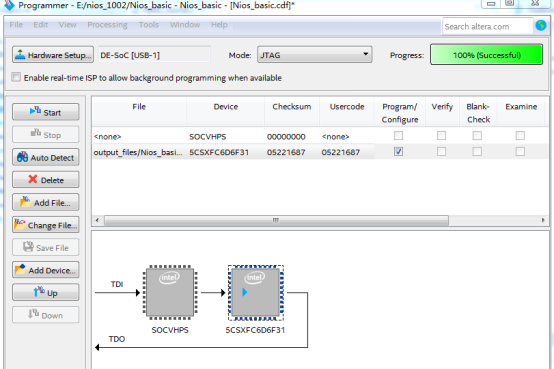

6.配置FPGA,将Quartus II编译后生成的.sof文件下载到FPGA中。使用USB下载电缆将开发板连接至PC机USB接口,然后打开开发板电源。回到Quartus II界面,单击“Tools| Programmer”,观察“Hardware Setup”是否为“DE-SoC[USB-1]”,如果是“No Hardware”,单击“Hardware Setup”,点击“Currently selected Hardware”,选择“DE-SoC[USB-1]”,点击“close”。将“Nios_Basic.sof”文件下载到FPGA中。下载界面如下图所示:

![]()

![]()

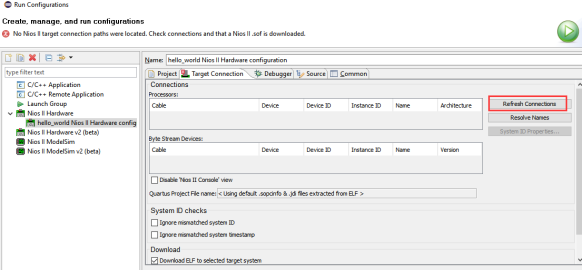

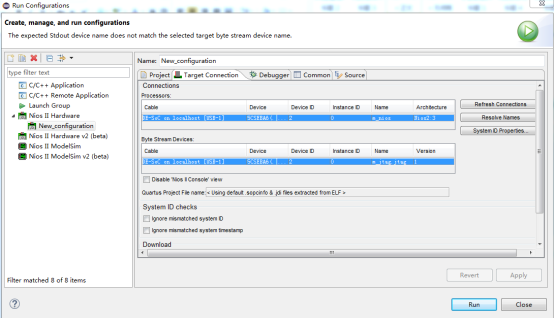

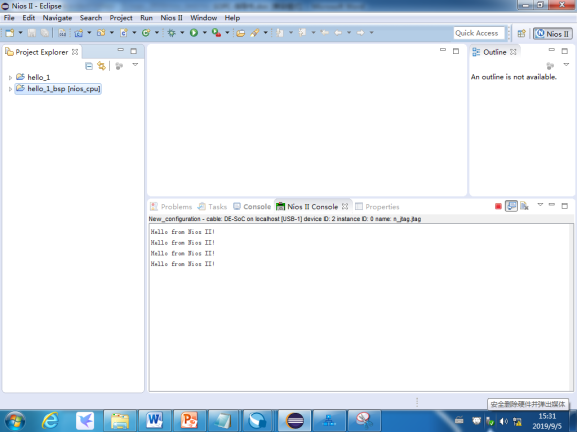

7. 配置NIOS,选择hello_world文件夹,点击右键,然后点击Run As-NiosII Hardware打开,得到如下图所示界面。在Project ELF file name中选择生产的elf文件

在出现No Nios II target connection paths were located. Check connections and that a Nios II .sof is downloaded.错误时,点击refresh connection,如下图所示。

7.单击Apply后,再单击Run,回到C语言编辑窗口,此时将C语言程序代码下载到目标电路板上,下载完成后,出现如图1-40所示“Hello from Nios II!”的字样,至此Hello World实验已经完成。

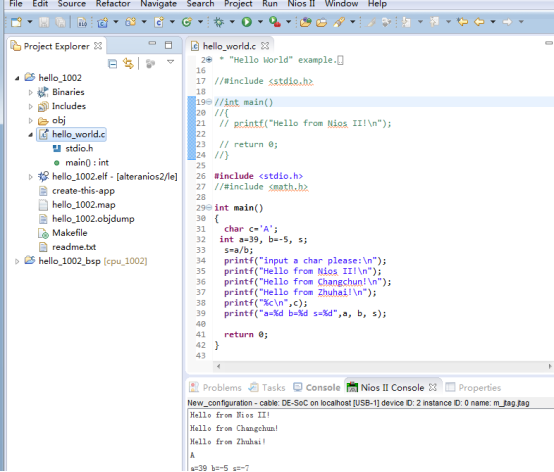

用户可以在程序增加简单的控制语句,增加对软核系统的领悟。如果要编写复杂的程序,特别是涉及到外设或者存储器件的编程请仔细参考Nios II提供的软件设计手册。

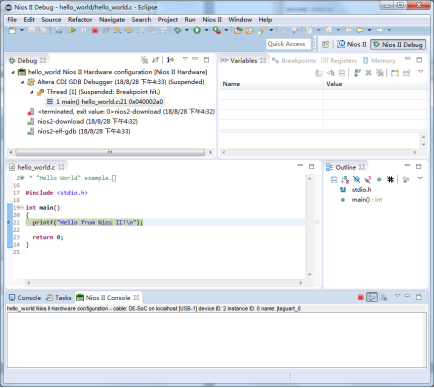

8.点击Debug As Hardware进入调试程序界面。

9.在Run菜单中可以设置复位,停止,断点,单步等调试运行方式。

在右侧各栏中可以查看变量,断点,寄存器,内存等的状态。

10、在串口调试助手中查看运行结果(下图的内容应显示在串口调试助手中)

10、修改hello_world文件,重新运行,可以得到下面的结果

四、实验报告(截图时,必须包含工程名与顶层文件名)

�������� 实验报告要求:

1. 实验内容、实验原理。

2. 给出NiosII嵌入式系统的连接图。

3. 给出Quartus Prime顶层设计原理图(包括工程名、顶层文件名、引脚配置)。

4. 给出Nios II IDE软件中的C语言程序。

5. 给出运行结果(可通过串口调试助手),其中包括个人的姓名与学号,同时可与个人签名学号同时拍照。

6. 请在文件首页附个人手写签名图片。

注意:

�������� 工程名与顶层文件名必须与姓名学号相关联

�������� 文件名:实验四_学号姓名